글쓴이 : SOONDORI

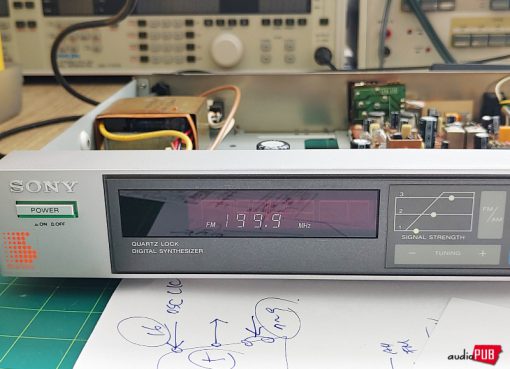

인터넷에서 CX-778A의 데이터 시트를 구할 수 없다. 그러면… PLL은 Black Box가 되고 그 동작을 장님 코끼리 만지기식으로 상상할 수밖에 없다는 이야기.

* 관련 글 : 일본 내수용 SONY ST-V5 튜너와 디지털 제어 시스템 (4)

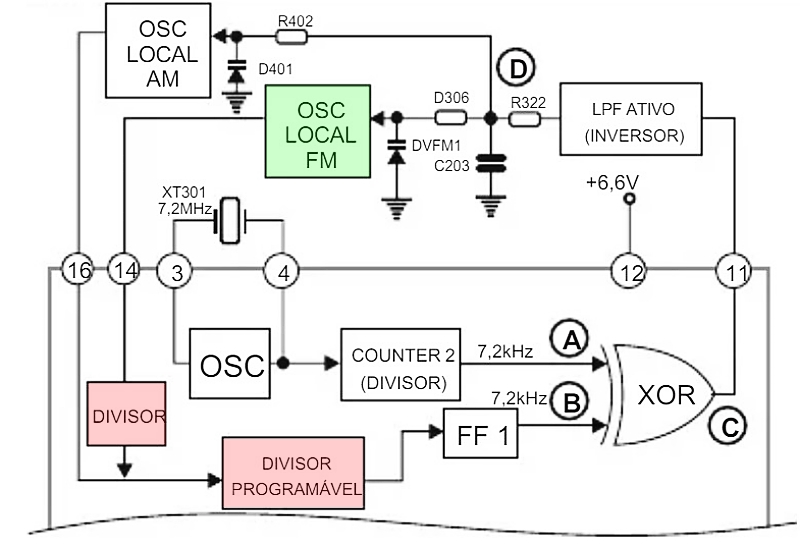

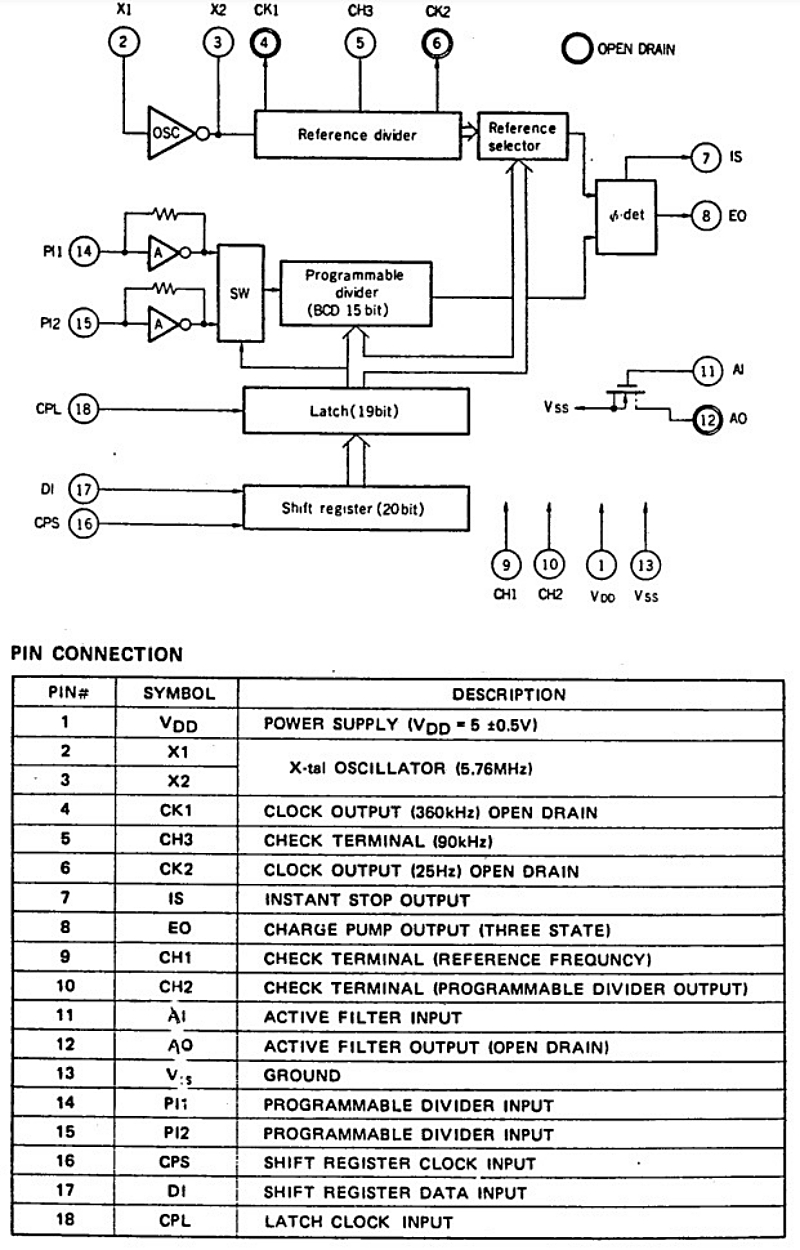

■ 전체 회로 구성

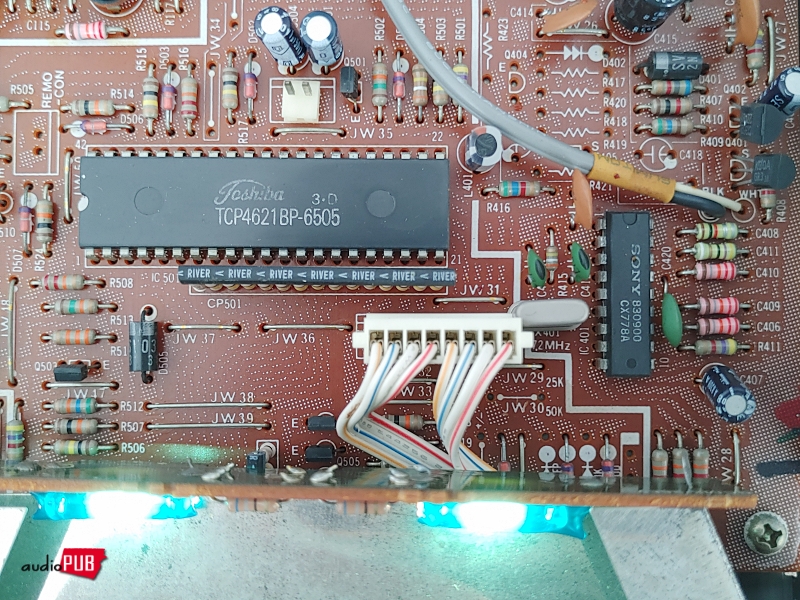

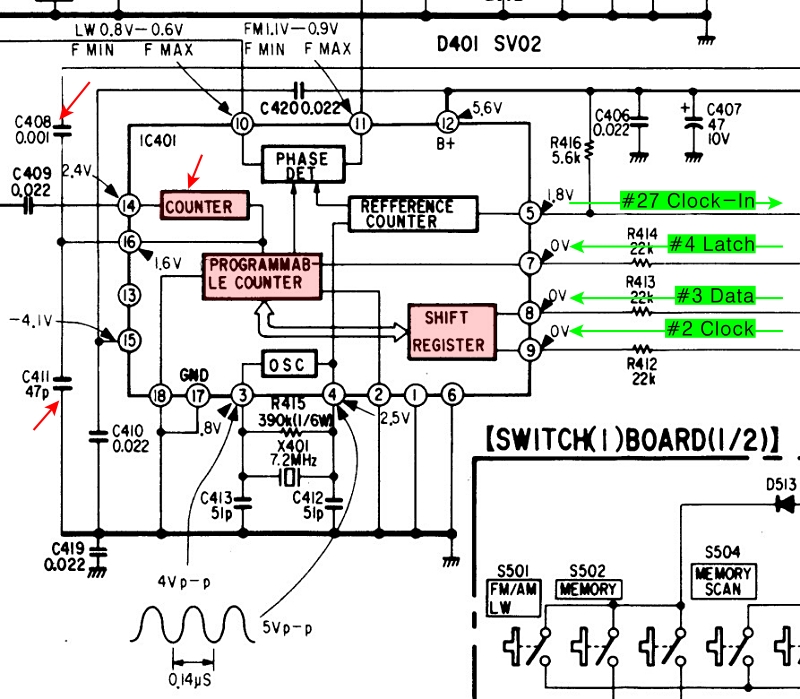

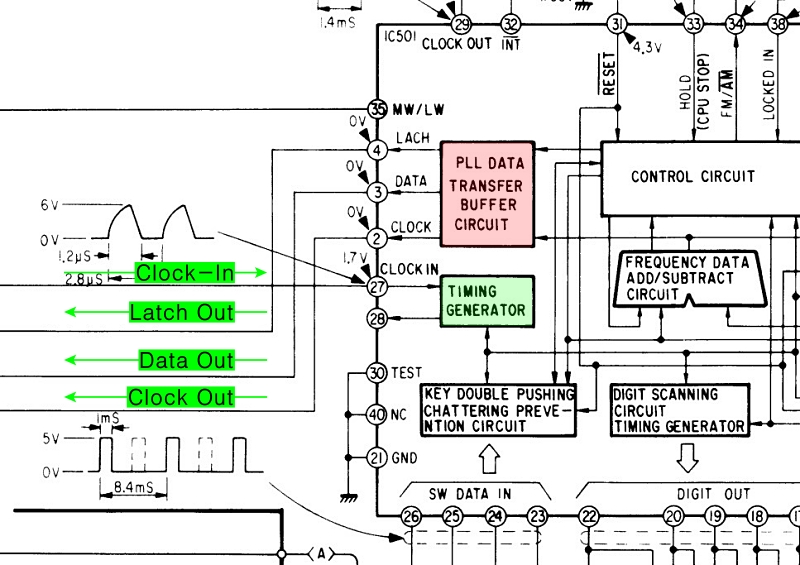

우선 PLL IC, 마이크로 컨트롤러 회로 영역의 구성은 다음과 같다.

(▲ #14는 프론트엔드 FM 클럭 입력, #16은 AM 클럭 입력, 현물에서 #10은 무시, #11은 PLL OUT)

이상에서 파악된 Flow는,

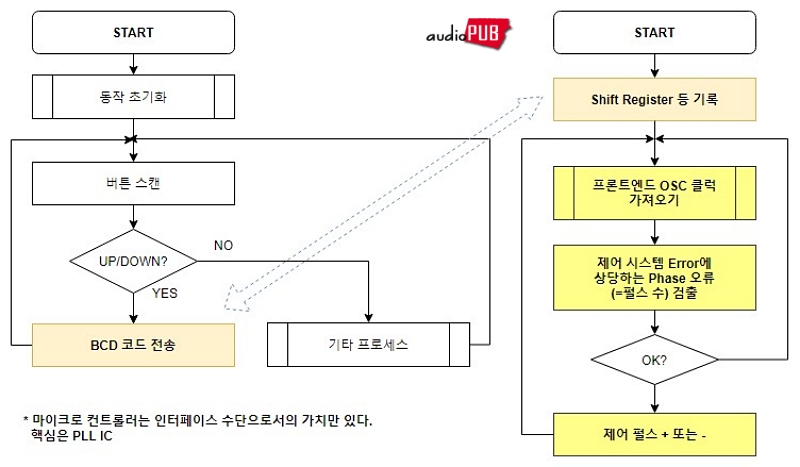

사용자 버튼 조작 → 마이크로 컨트롤러가 VFD 숫자 표시 + 동시에 적당한 목표 주파수의 16비트 시리얼 데이터를 PLL IC에 1회 단발성 전송 → PLL IC가 데이터를 <Programmable Counter 블록>에 설정 → PLL IC가 적당한 펄스를 생성하고 이후 적산기 작용에 의해 프론트 엔드 통제전압 변경 → PLL IC가 프론트엔드 피드백 클럭을 받고 기 설정된 목표 주파수와 비교 → PLL IC가 스스로 목표 대 에러를 보정한다. 즉, 제어명령 전송 후 마이크로 컨트롤로는 아이들 상태로 대기.

대체로 마이크로 컨트롤러가 어떤 값을 던져주기만 하면 나머지는 PLL IC가 다 알아서 처리하는 흐름이다. 단방향 처리라는 게 즉, 완벽한 폐루프 제어가 아니라는 것이 조금 이상한데… 뭔가 그럴듯한 게 없는지?

(시간 흐른 후)

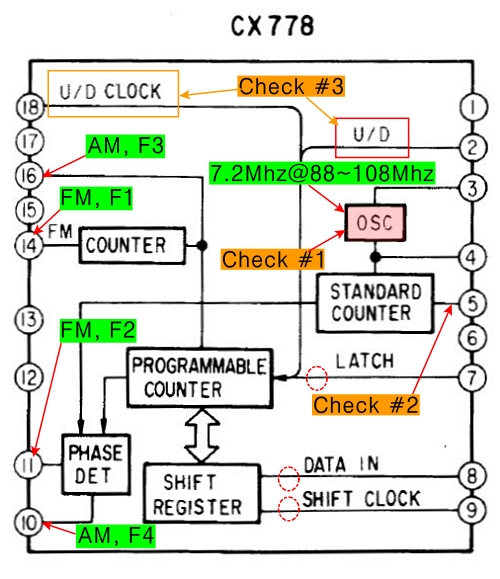

■ PLL IC 내부

PLL IC의 핵심인 Phase Detection 즉, 목표 주파수와 현재 주파수 카운팅, 에러 도출과 보정은 아래와 같이 처리되는 모양이고…

역시 PLL IC의 데이터 시트가 없어서 좀 답답한 상황인데… 인터넷을 더 뒤졌고 일본 KAZE 님이 올려주신, 나름 보기 편한 블록도를 찾아냈다.

(출처 : http://nice.kaze.com/av/st-s555es.html)

상상을 더하여 궁리해보면,

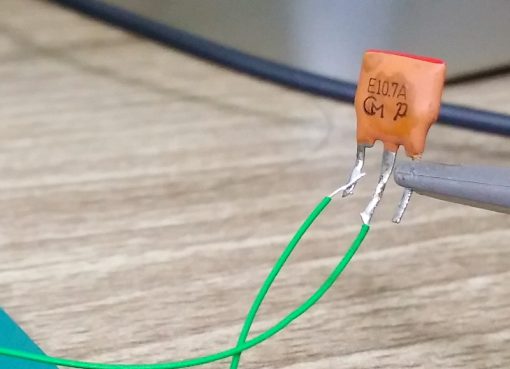

1) Check #1 : 표준 회로도의 OSC Clock은 7.2Mhz, 현물도 7.2Mhz.

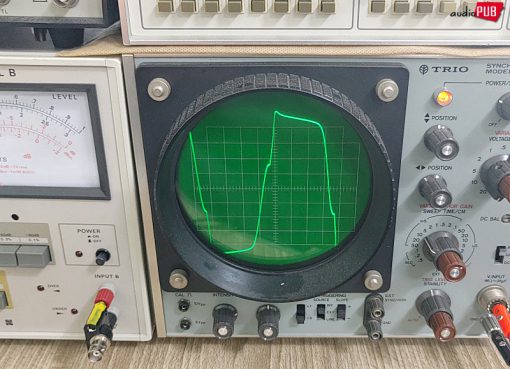

2) Check #2 : #5핀에 OSC 7.2Mhz를 분주한 어떤 펄스가 출력될 것처럼 보인다. 실제로 그런가? → 마이크로컨트롤러 동작용 360Khz 단일 클럭이 출력된다. 전편 글에서 언급한 갑작스러운 Dial Span 확장은 PLL #5핀~마이크로 컨트롤러 라인에서 프로브 접촉에 의한 펄스 유실 때문에 생긴 오류. (실제로 반복 재현할 수 있다)

3) #14핀~<Counter 블럭>~<Programmable Counter 블럭> 구조에서, Programmable 키워드가 변수로 작용하면 PLL 동작이 달라질 것이다. 변수는 Latch, Data-In, Shift Clock 세 요소에 의한 어떤 설정이겠고 그것은 마이크로 컨트롤러가 정하는 것.

4) Check #3 : U/D Clock은 Up/Down Clock의 줄임말일 것. 그러므로 우격다짐 수동 조작도 가능할 것으로 보이고… 표준 회로도에서는 두 핀을 묶어서 GND에 연결하고 있다. 그런데 마침 마이크로 컨트롤러에서 제어 펄스를 받는 <#7 Latch>가 #2, #18에 연결되니까 결국 Latch는 GND에 묶인, 즉, Pull-Down에 의한 Disable 상태인 것처럼 보인다. 정말 그런가? → NO. 논리적인 묘사일 뿐 물리적으로는 아무 관련 없음.

(시간 흐른 후)

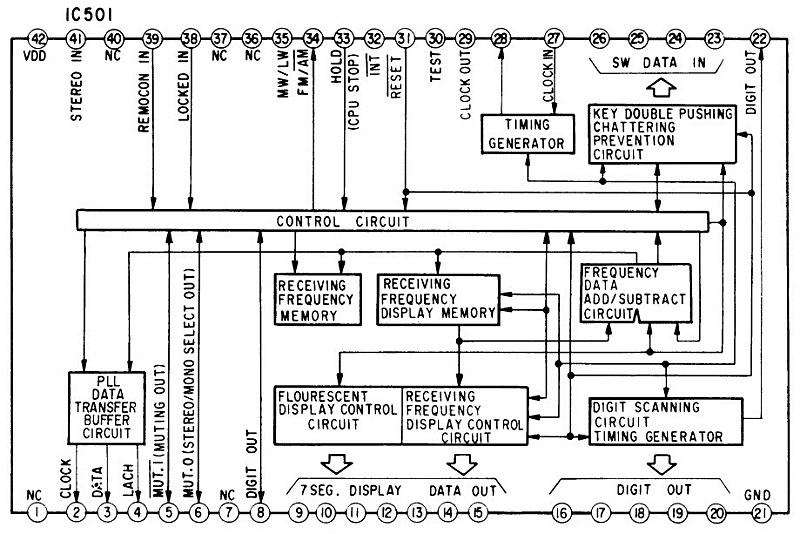

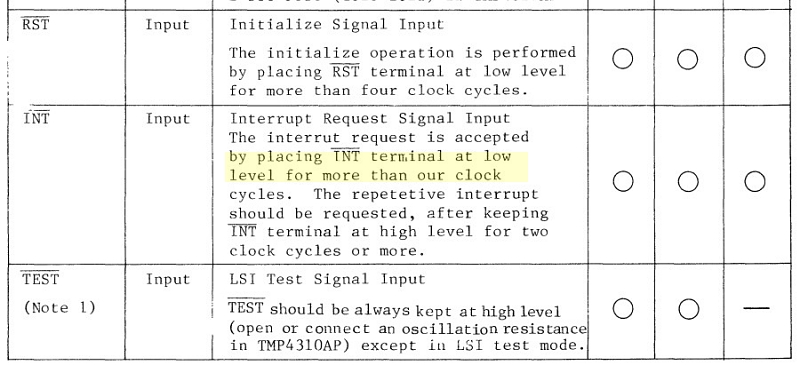

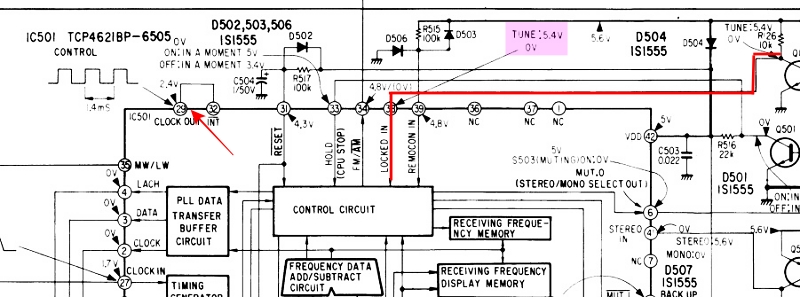

■ 마이크로 컨트롤러 CLOCK OUT과 INT

Clock Out 클럭은 700hz. 그것을 인터럽트 핀으로 받은 다음, 마이크로 컨트롤러 내부 프로시저 처리에 활용하는 것으로 추정된다. 예를 들어 1/700초 주기의 주기적인 버튼 스캔 같은 것?

(시간 흐른 후)

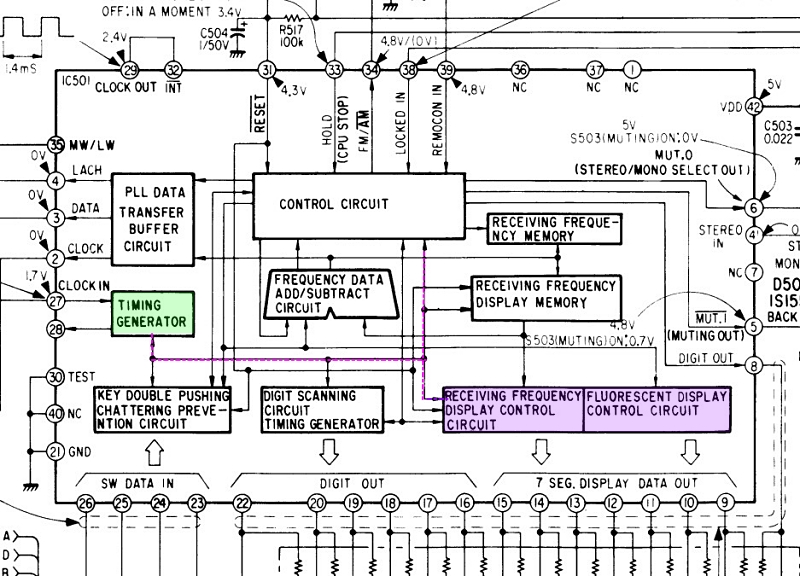

■ 마이크로 컨트롤러 SIGNAL LOCKED

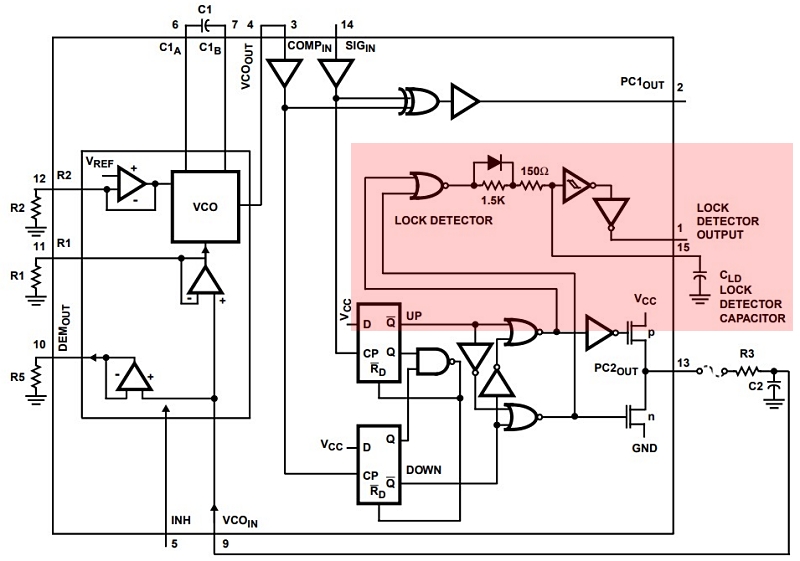

TI社 PLL IC 데이터 시트를 차용하여 PLL IC의 내부 동작을 추정해보면… 아래에서 두 주파수 비교 처리의 핵심은 <Lock Detector 블록>일 것인데 CX-778A에서는 <Programmable Counter 블록>으로 정의하고 있다.

Texas Instruments CD74HC7046A 데이터 시트

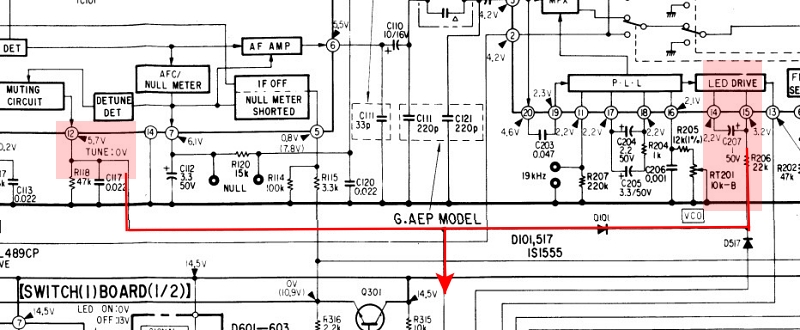

Locked… 그 키워드로 아래 회로도를 살펴보면 1) IF IC <Muting Circuit 블럭>, 2) MPX IC <LED Driver 블럭>이 마이크로 컨트롤러 ‘Locked In’ 핀에 연결되어 있다.

프론트엔드 이후 신호 처리 상태를 보고 VFD에 ‘Locked’ 문자 점등 또는 소등하는 기능으로 이해하고 PASS.

(시간 흐른 후)

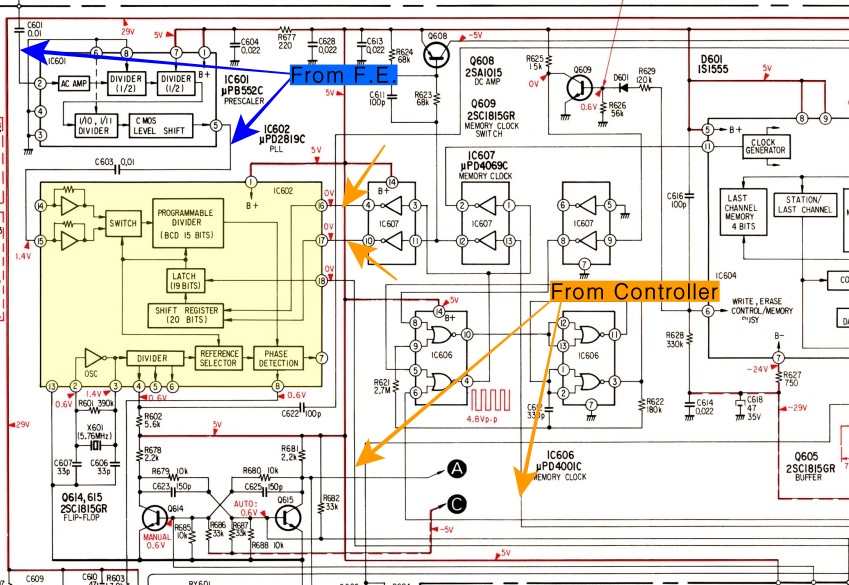

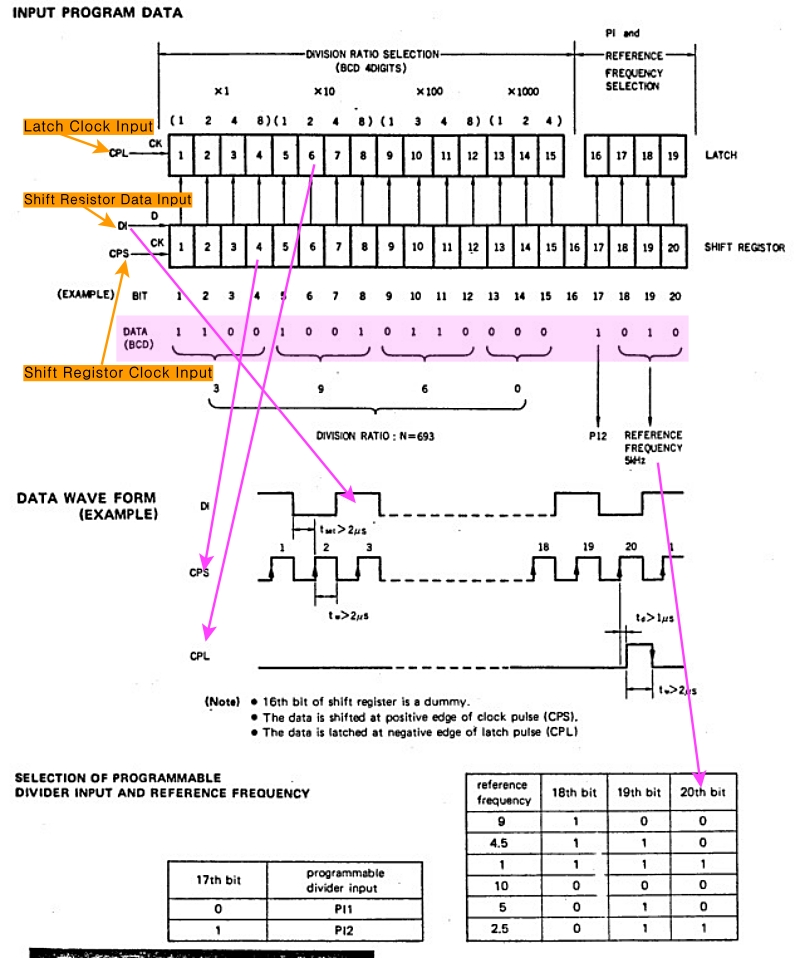

■ 비교용 NEC uPD2819C PLL IC

어떤 제어 명령이, 어떻게 처리되는가?

ST-V5 데이터 시트에는 ’16비트 시리얼 데이터를 쓴다”는 단서 한 줄만 적혀 있다. 그래서 뭘? 할 수 없이 1970년대 말에 소개된 SONY ST-P7J 튜너의 데이터 시트를 구해서 살펴보았고…

1) Latch, Shift Register, Programmable Diver 블럭의 취급 데이터는 BCD(Binary-Coded Decimal, 이진화 십진법) 체계의 것, 2) 그것은 흔히 십진수로 예시되는 목표 주파수가 아니라 프론트엔드 피드백 클럭의 비교에 관련 된 제반 분주(Scaler, Divider)의 비율을 정하는 BCD 값이며, 3) Shift Registor 세팅이 기본이다, 4) 해석 규격은 아래와 같이 정리된다.

이상의 운용 프레임은 ST-V5에 유추 적용할 수 있을 것.

WHY? 그 밥에 그 콩나물이고… 그 시절의 소니가 굳이 BCD를 쓰는 마이크로 컨트롤러 세상을 뛰쳐나갈 이유는 없으니까. 사실, 미국 원천 솔루션의 엿보기로 뭘 만드는 정도였을 터이니 그럴 능력은 안 되었을 것이다.

글이 너무 길어졌기에… 기록해둔 각 핀 펄스 파형, PLL 및 마이크로 컨트롤러의 특이 동작, 간단한 테스트, 추정한 로직 등은 다음 글로 이어서 정리한다.

* 관련 글 : 일본 내수용 SONY ST-V5 튜너와 디지털 제어 시스템 (6)